# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & MANAGEMENT COMPARISON OF THE REDUCED NUMBER OF SWITCHING ELEMENTS MULTILEVEL INVERTERS

# Abdulvehhab Kazdaloglu<sup>\*1</sup>, Bekir Cakir<sup>2</sup>, Kutay Is<sup>3</sup> & Aziz Guneroglu<sup>4</sup>

\*1,2,3&4 Department of Electrical Engineering, Faculty of Engineering, Kocaeli University, Kocaeli, Turkey

#### ABSTRACT

In this study, the multi-level inverter is supplied with asymmetric sources, the output voltage wave patterns of change were examined. Also, unlike other applications in the literature R (resistive) load, except RL (resistive-inductive) that may be in the form of output voltage waveforms in case of load changes are examined.

Keywords: Inverter, multilevel, symmetric, asymmetric, load.

## I. INTRODUCTION

Multilevel inverters, has attracted first developed in 1924 by Erwin Marx and attention with a high voltage circuit known as the Marx generator. As a result of studies of the mathematical modeling of Multilevel inverter systems is easier to do the simulation of Inverters[1,2]. The objective of multilevel inverters is increasing the number of levels to obtain a voltage waveform close to pure sinusoidal. For this purpose, a number of studies have been made [3].

When the number of inverter level is increased, the output voltage is close to the sine shape and thus inverter can feed more sensitive loads, such as induction motor drives [4]. Multilevel inverters are used to connect the renewable energy sources producing DC voltage to the network. [5]. Unlike the Traditional multi-level inverter topologies the new topologies can be seen in the literature One of these new topologies is the asymmetrical hybrid multilevel inverter topology. This topology is obtained by using H-Bridge with three known topologies (diode clamping, flying capasitor is, cascade) [6].

One of the main problems of multilevel inverters is contain a large number of switching elements and the difficulty of controlling these components. For this purpose, studies for reducing the number of the switching element have been made [7].

In this study, multi-level inverter topology is obtained by reducing the number of switching elements compared in different feeding conditions and at different load conditions, and the results was investigated.

# II. THE COMPARISON OF INVERTER TOPOLOGIES, FOR SYMMETRIC AND ASYMMETRIC FEEDING CONDITION

In the literature a lot of multi-level inverter topologies, such as Diode clamped, Capacitor clamped (flying capasitor) and H-bridge, are recommended. Here, we will examine the cascaded H bridge topology applications, which are reduced the number of switching element.

the symmetric and asymmetric multilevel inverters supply situation and resistive R (38 $\Omega$ ), ohmic-inductive and RL (R = 38 $\Omega$  L = 28mh) load cases were examined below.

#### A. Topology 1

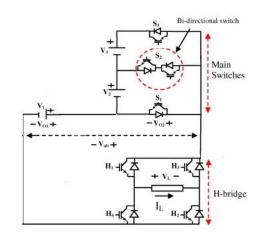

Topology applied to reduce the number of switching elements is shown in Figure 1. In the figure, S1 and S3 unidirectional switching elements, the switching element S2 is bidirectional. S2 switch blocking voltage while providing bidirectional current flow [8].

Figure 1: New topology obtained by reducing the number of switching elements [8]

$$V_{max} = V_1 + V_2 + V_3$$

(1)

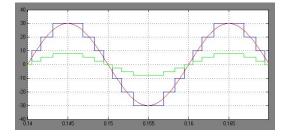

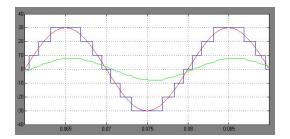

When the Circuit topology is simulated under R ( $38\Omega$ ) and RL (R =  $38\Omega$  L = 28mh) load. The Output voltage and current waveforms are shown. The harmonic distortion of voltage and current values occur under this load (VTHD, Ithd) is given under the figures.

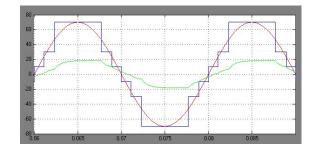

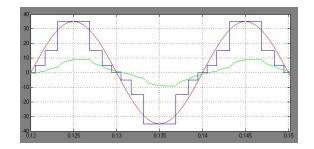

Figure 2: Reduced the number of switching element 7 level inverter output voltage and current waveforms with R load.  $V_{THD}=I_{THD}=12\%$

Figure 3: Reduced the number of switching element 7 level inverter output voltage and current waveforms with RL load, V<sub>THD</sub>=12% I<sub>THD</sub>=3.5%

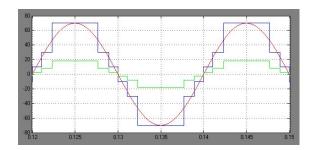

If we use an asymmetric feed for the same topology, theoretical, output level reaches 13. But in this topology, the feed situation of asymmetric source V1 will be activated in any case is not suitable for this topology. For 13 level status; Level 1, Level 3 and Level 6 is formed in positive alternans. Due to the nature of the topology, the 2, 4 and 5 levels are not formed. the fact that instead of the 13-level inverter for asymmetric supply situation is realized as 6 levels. Asymmetrical multilevel inverter-fed output voltage and current waveforms in the case of variable load are shown below.

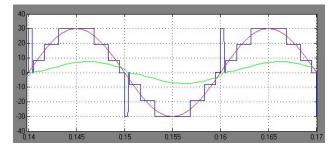

Figure 4: Reduced the number of switching element 7 level inverter output voltage and current waveforms with R load.  $V_{THD}=I_{THD}=16\%$

Figure 5: Reduced the number of switching element 7 level inverter output voltage and current waveforms with RL load,  $V_{THD}=16\% I_{THD}=7\%$

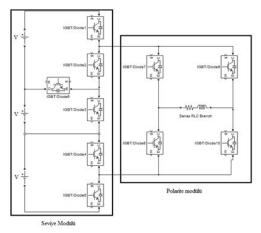

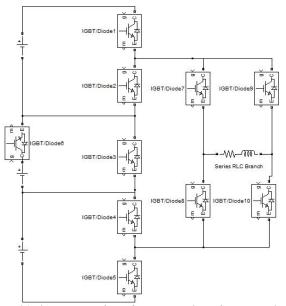

### B. Topology 2

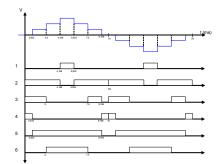

A symmetrically fed 7-level inverter topology, applied to reduce number of switching elements, is given in figure6 [9]. 6 IGBTs are used in this topology as the switching element. For the Inverter topology is given in Figure 6, the output voltage waveform, the voltage waveform transmission ranges of IGBTs and IGBT drive circuits for the formation of the output voltage waveforms are given in Figure 7-8-9-10.

Figure 6 : Symmetrically fed 7-level inverter topology [9]

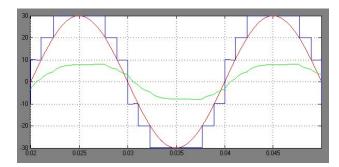

Figure 7: 7-level inverter output voltage waveform for the IGBT conduction conditions. [9]

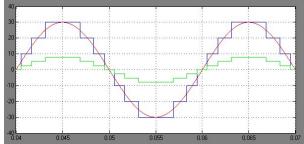

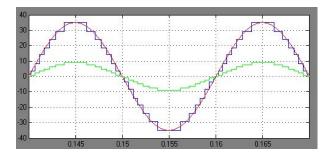

Figure 8: 7-level inverter output voltage and current waveforms with R load, V<sub>THD</sub>=I<sub>THD</sub>=17%

Figure 9: 7-level inverter output voltage and current waveforms with RL load, V<sub>THD</sub>=17% I<sub>THD</sub>=10%

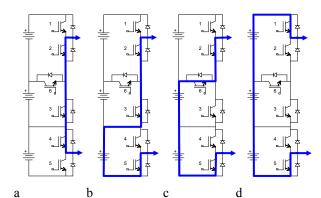

Figure 10: a) The inverter output 0 level. (2 - 3 - 4 IGBTs transmission condition). b) The inverter output 1 level (2 - 3 - 5 IGBTs transmission condition)c) The inverter output 2 level (2 - 6 - 5 IGBTs transmission condition)d) The inverter output 3 level (1 - 5 IGBTs transmission condition) [9]

**INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & MANAGEMENT**

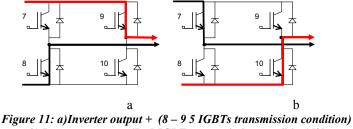

The important point to note here, the 2 IGBT that control each voltage source should not transmit at the same time. For each case, Only one of 2 IGBTs is in transmission condition. In addition, The output voltage polarity of this inverter topology is controlled by a separate H-bridge IGBTs group. H-bridge IGBT group and IGBTs conduction conditions are given in figure 11.

b) Inverter output – (7 – 5 IGBTs transmission condition)[9]

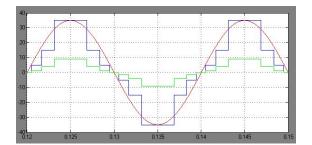

If we use an asymmetric feed for the same topology, theoretical, output level reaches 15. switching states for the 15 level is; IGBT switching states of the expulsion of Table 1 are met taking into account the output voltage and current waveforms occur is given in Figure 12-13.

| Output Level | IGBTs With Transmission |

|--------------|-------------------------|

| 0            | 2-3-4                   |

| 1            | 2-3-5                   |

| 2            | 2-6-4                   |

| 3            | 2-6-5                   |

| 4            | 1-6-3-4                 |

| 5            | 1-6-3-5                 |

| 6            | 1-4                     |

| 7            | 1-5                     |

TABLE 1: Possible switching states for the state of the asymmetric feeding

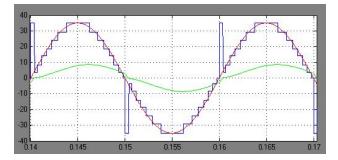

Figure 12: The asymmetric feeding ouput voltage and current waveforms with R load,  $V_{THD}=I_{THD}=27\%$

Figure 13: The asymmetric feeding ouput voltage and current waveforms with RL load,  $V_{THD}=27\% I_{THD}=18\%$

In case of asymmetric feed, the 4, 5 and 6 level does not occur. after the 3rd Level, is skipped to 7th level. In this case the voltage output is out in the form of sine .

#### C. Topolgy 3

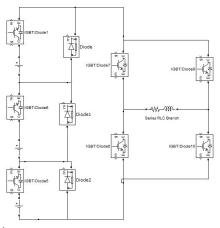

In this topology without changing the number of switch, If the place of IGBTs changes, a topology for asymmetric feeding will be obtained. If the IGBT-6 location is changed and connected in series with the indicated source of 2V, this problem will be eliminated. The topology is obtained by changing the position of the IGBT-6 is shown in Figure 14.

Figure 14: inverter topology for symmetric and asymmetric feeding

If the feed of the inverter's used in this topology sources is selected in equal size (symmetric), the output will be 7 levels.

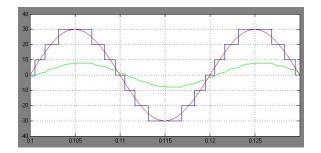

Figure 15: The symmetric feeding ouput voltage and current waveforms with R load,  $V_{THD}=I_{THD}=12\%$

40 INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & MANAGEMENT

Figure 16: The symmetric feeding ouput voltage and current waveforms with RL load, V<sub>THD</sub>=12% I<sub>THD</sub>=3%

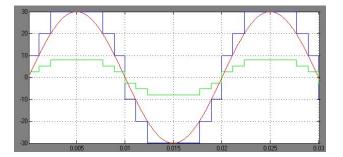

If asymmetric (2n, 1-2-4 as the exponent multiples of 2) is selected, the output will be 15 levels. Simulation results for the asymmetric feeding situation in the same topology are given below.

Figure 17: Asymmetric feeding 15 level inverter topology output voltage and current waveforms with R load,  $V_{THD} = I_{THD} = 5.5\%$

Figure 18: Asymmetric feeding 15 level inverter topology output voltage and current waveforms with RL load,  $V_{THD}$ =5.5%  $I_{THD}$ =1%

## D. Topolgy 4

Using Diode instead of IGBTs connected in parallel to the resources of DC was obtained the 15 simplified multilevel inverter topologies are also available. [10]. But these studies, only R (resistive) load is specified for the ideal. The simulation results are given below for Asymmetric supply situation in the same topology.

Figure 19: İnverter topology for symmetric and asymmetric feeding

Figure 20: The symmetric feeding ouput voltage and current waveforms with R load, V<sub>THD</sub>=I<sub>THD</sub>=13%

Figure 21: The symmetric feeding ouput voltage and current waveforms with RL load, V<sub>THD</sub>=27% I<sub>THD</sub>=8%

Figure 22: Asymmetric feeding 15 level inverter topology output voltage and current waveforms with R load,  $V_{THD} = I_{THD} = 6\%$

Figure 23: Asymmetric feeding 15 level inverter topology output voltage and current waveforms with RL load,  $V_{THD}=26\%$  $I_{THD}=7\%$

# **III. CONCLUSION**

In this study, reduced the number of switching elements of multi-level inverter output voltage and current waveforms change with different feed voltages and different load cases were examined. The objective of multilevel inverters, as far as possible the output the approximation is to pure sine shape therefore minimize the ITHD and VTHD. Firstly, the number of switching elements in the literature topologies were compared according to different feeding conditions and situations to work in different load conditions. The comparison results are given in table 2.

| Table 2. Inventor tonalogia  | according to the co    | manican of current | nia acusana stuil fa | ading and DI load  |

|------------------------------|------------------------|--------------------|----------------------|--------------------|

| Table 2: Inverter topologies | s accoraing to the col | mparison oj symmei | пс-азуттеник је      | eaing ana KL ioaa. |

| Topology | Number<br>of IGBT | Number<br>of Diode | Symmetric<br>Feeding | Asymmetric<br>Feeding | R-L load |

|----------|-------------------|--------------------|----------------------|-----------------------|----------|

| 1        | 4                 | -                  | P                    | Х                     | Ł        |

| 2        | 6                 | -                  | P                    | Х                     | R        |

| 3        | 6                 | -                  | P                    | R                     | R        |

| 4        | 3                 | 3                  | Þ                    | Х                     | Х        |

Subsequently, the ITHD and VTHD values are compared for the investigated topologies. The resulting values of Table 3 were obtained.

| Table 3: Inverter topologies according to the comparison of symmetric-asimerik feeding and total harmonic distortion with R |

|-----------------------------------------------------------------------------------------------------------------------------|

| and RI load                                                                                                                 |

| Feeding    | Topology | Level | R    |                  | RL   |                  |

|------------|----------|-------|------|------------------|------|------------------|

|            |          |       | VTHD | I <sub>THD</sub> | VTHD | I <sub>THD</sub> |

| ric        | 1        | 7     | 12   | 12               | 12   | 3,5              |

| let        | 2        | 7     | 17   | 17               | 17   | 10               |

| Symmetric  | 3        | 7     | 12   | 12               | 12   | 3                |

| Syl        | 4        | 7     | 13   | 13               | 27   | 8                |

| ic         | 1        | 7     | 16   | 16               | 16   | 7                |

| etr        | 2        | 7     | 27   | 27               | 27   | 18               |

|            | 3        | 15    | 5,5  | 5,5              | 5,5  | 1                |

| Asymmetric | 4        | 15    | 6    | 6                | 26   | 7                |

\*ITHD and VTHD values in the table are given in %

As a result of simulation studies for 4 topology examined in this study, The 3rd topology called MultiSource Topology in the literature is found to be the optimal topology for symmetrical-asymmetrical feed conditions and variable load conditions. Simulations conducted for this topology, the ITHD value IEEE1547 standard, well below 5% occurred in 1%

#### REFERENCES

- [1] Twining, E., Holmes, D.G., "Voltage Compensation In Weak Distribution Networks Using Multiple Shunt Connected Voltage Source Inverters", Power Tech Conference Proceedings, 2003, IEEE Bologna,

- [2] C. Cecati, A. Dell'aquila, M. Liserre: "A novel three-phase single-stage distributed power inverter", IEEE Transactions on Power Electronics, Vol.19, No.5, September 2004, pp.1226–1233, ISSN 0885-8993

- [3] Teichmann, R.; Bernet, S:" A Comparison Of Three-Level Converters Versus Two-Level Converters For Low Voltage Drives, Traction, And Utility Applications", IEEE Trans. on Industry Applications, May-June 2005, pp.855 - 865

- [4] Farid Khoucha, Soumia Mouna Lagoun, Khoudir Marouani, Abdelaziz Kheloui, and Mohamed El Hachemi Benbouzid, "Hybrid Cascaded H-Bridge Multilevel-Inverter Induction-Motor-Drive Direct Torque Control for Automotive Applications", IEEE Transactions On Industinal Electronics, Vol. 57, No. 3, March 2010

- [5] Thorsten Bulo, Benjamin Sahan, Christian Nöding, Peter Zacharias, "Comparison Of Three-Phase Inverter Topologies For Grid-Connected Photovoltaic Systems", 22nd European Photovoltaic Solar Energy Conference and Exhibition, 3 - 7 September 2007, Milan, Italy.

- [6] E. Özdemir, Ş. Özdemir, L.M. Tolbert, "Fundamental Frequency Modulated Six-Level Diode-Clamped Multilevel Inverter for Three-Phase Stand-Alone Photovoltaic System" IEEE Transactions on Industrial Electronics, Vol. 56, No. 11, November 2009. pp. 4407-4415

- [7] Najafi E., Yatim A.H.M., Samosir A.S., "A New Topology -Reversing Voltoge (RV)- for Multi Level Inverters", 2nd IEEE International Conference on Power and Energy, December 1-3 2008, Malaysia

- [8] M.R. Banaei, E. Salary "New multilevel inverter with reduction of switches and gate driver", Energy Conversion and Management. Proceedings of ICEE 2010, May 11-13, 2010

- [9] Ehsan Najafi, Abdul Halim Mohamed Yatim, "Design and implementation of a new multilevel Inverter topology", IEEE Transactions On Industrial Electronics, Vol. 59, No. 11, November 2012

- [10] Sarikurt, T.; Ozturk, O. Balikci, A. "Simplified Multilevel Inverter Model and Its Control with Selective Harmonic Elimination Method", Electrical, Electronics and Computer Engineering (ELECO), 2010 National Conference on 2-5 Dec. 2010, pp. 283-287